OrCAD / Allegro Release 17.4 QIR1

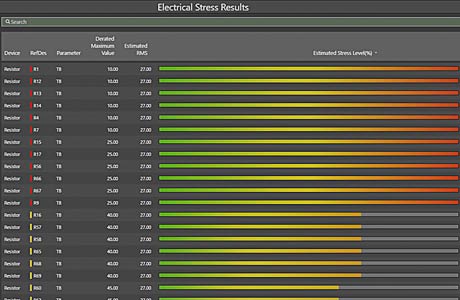

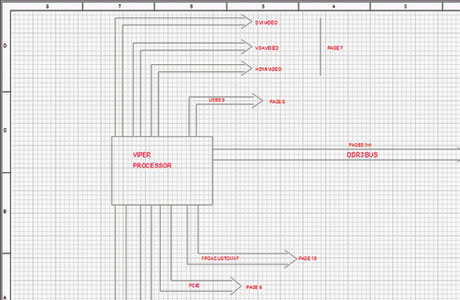

Die neue Version OrCAD / Allegro 17.4 QIR1 wurde Anfang Juni 2020 veröffentlicht. Sie enthält eine Reihe von Verbesserungen für das effiziente Design von Leiterplatten. Dies umfasst Verbesserungen der Benutzerfreundlichkeit basierend auf Benutzerfeedback sowie ein modernisiertes Erscheinungsbild des PCB Editors. System Capture liest nun OrCAD Capture Bibliotheken und ist kompatibel mit der CIS-Bibliotheksschnittstelle. In System Capture gibt es eine Zuverlässigkeitsanalyse ohne Modelle. Sie können System Capture mit jeder Allegro Schematic Entry-Lizenz verwenden.

Dies sind die wesentlichen neuen Features:- Umgebung für ausführbare Designregeln

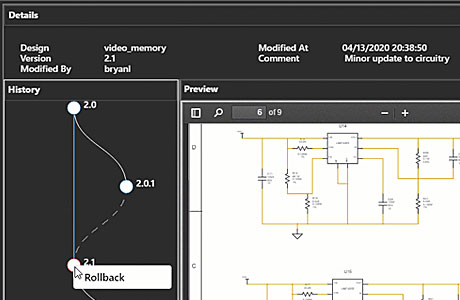

- Eingebettete native Datenverwaltung

- Intelligentes PDF in allen Modulen

- Leistungsverbesserungen im PCB Editor

- Neue DFM-Regeln für Microvias

- Optimierung des interaktiven 3D-Canvas