Allegro High-Speed Option

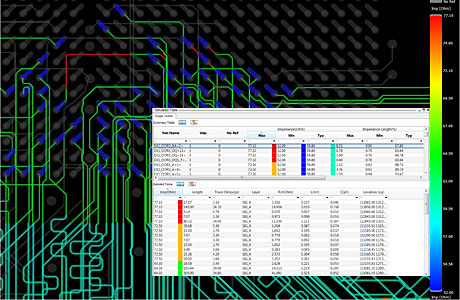

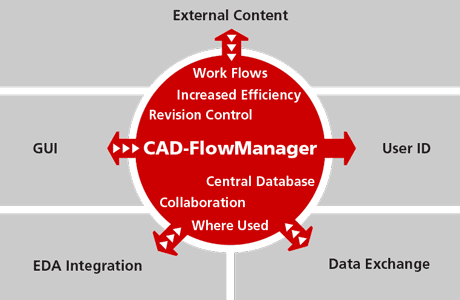

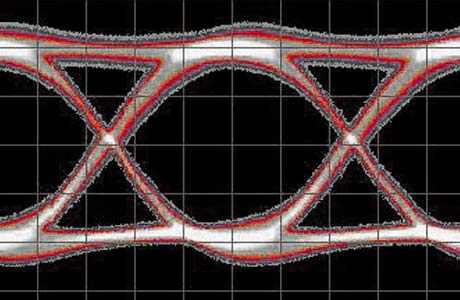

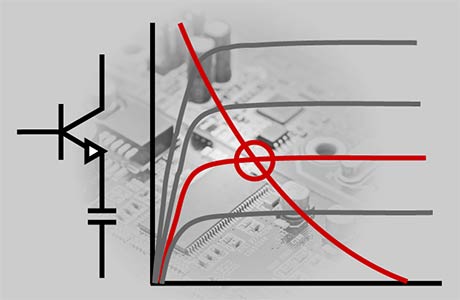

Increasing use of standards-based advanced interfaces such as DDR3, DDR4, PCIe, USB 3.0 are bringing a set of constraints that must be adhered to while implementing a PCB. The Allegro PCB Designer High-Speed Option makes adhering to constraints on advanced interfaces quick and easy. It offers an extensive range of electrical rules to ensure that the PCB design implementation is complaint with the specification for advanced interfaces. Additionally, it allows users to extend the rules through the use of formulas with existing rules or post-route data such as actual trace lengths.

The High-Speed Option allows users to apply a topology to a set of signals. A topology can include a set of routing preferences as well as constraints such as putting the termination resistor closer to either the driver or a receiver on a signal. The constraint-driven PCB design system then provides feedback through the constraint manager if a signal doesn’t conform to the topology or the rules associated with the topology, ensuring that issues are identified (and therefore can be addressed) as quickly as possible. The High-Speed Option also enables checking of delays through vias, connector pins, and IC package-pin for die2die length/delay matching. It includes, utilities to identify trace segments crossing voids (return path issues that cause re-spins), supports back drilling (remove through hole antennas) as well as provides a timing environment that can accelerate timing closure of critical nets up to 60-70% .

- Timing vision

- Auto-interactive Delay Tuning

- Constraint Manager: Electrical rule set (reflection, timing, crosstalk)

- Electrical Constraint Sets – ECSets / Topology Apply

- Constraint-driven flow using electrical rules

- Electrical constraint rule set (ECSets) / topology apply

- Formula and relationship-based (advanced) constraints

- high-speed via structure

- Return path management for critical signals

- Spread segments between voids (DFF)

- Re-size/Re-space Diff Pairs