OrCAD / Allegro Release 17.4 QIR1

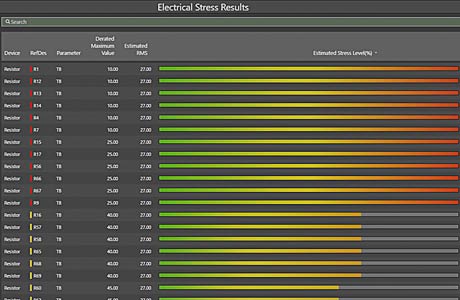

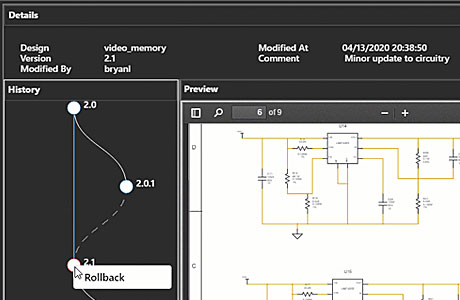

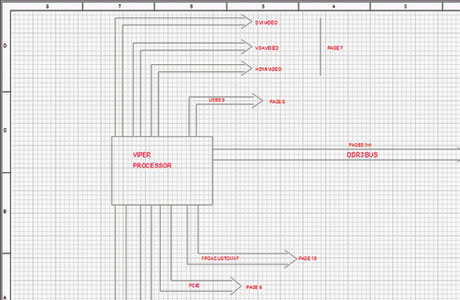

OrCAD / Allegro 17.4 QIR1 was released in early June 2020. It includes a variety of improvements for professional design of printed circuit boards. This includes usability improvements based on user feedback as well as a modernized look and feel of PCB Editor. System Capture will from now on read OrCAD Capture libraries and is plug compatible to the CIS library interface. In System Capture there is a reliability analysis without any models integrated. Users can try and use System Capture with any Allegro Schematic Entry license.

These are the main new features:- Enabling executable constraint ecosystem

- Embedded native data management

- Intelligent PDF out in all tiers

- Performance improvements in PCB Editor

- New DFM rules for microvias

- Interactive 3D canvas improvements