Allegro System Capture

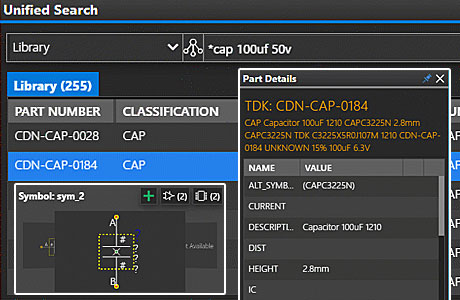

Define the architecture of a design with a smooth implementation to create a product that meets cost, performance, and formfactor requirements. Cadence Allegro System Capture is a scalable and easy-to-use solution for fast design intent creation that allows the high-level system architecture and functional diagram to stay connected to the detailed implementation of each board.

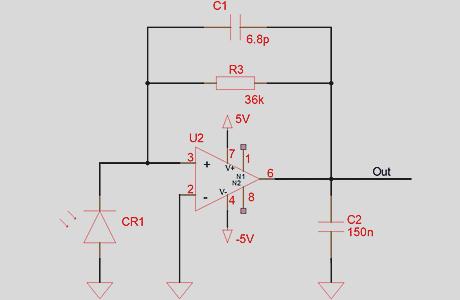

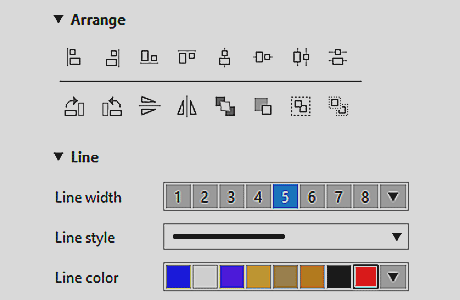

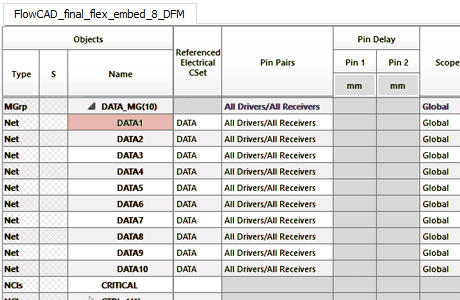

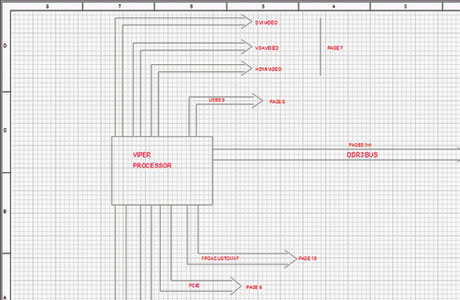

Start with definition and functional block diagrams to define the architecture of your electronic set-up and apply design constraints on system level as needed. Use hierarchical blocks to partition your design and generate designs context for multiple printed circuit boards in a framework and keep them all in sync. All settings are available in preferences dialog box for configuration.

- System Definition and Functional Block Diagrams

- Partitioning and Assembly Integrity

- System Connectivity Integrity

- Signal Traceability

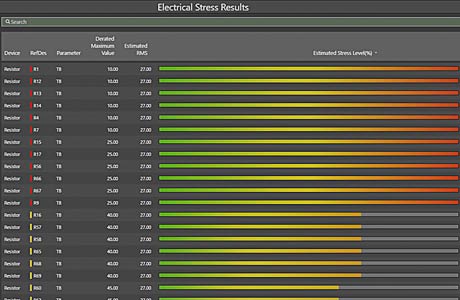

- Schematic Validation

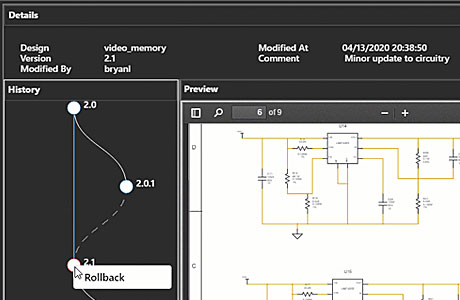

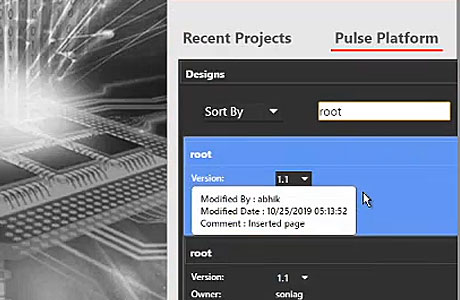

- Concurrent Team Design

- Reliability Analysis without Models