FloWare Toolbox

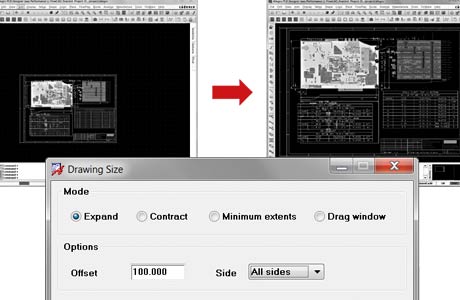

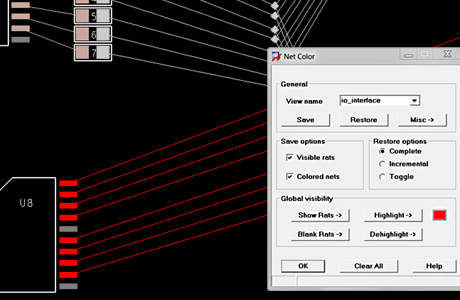

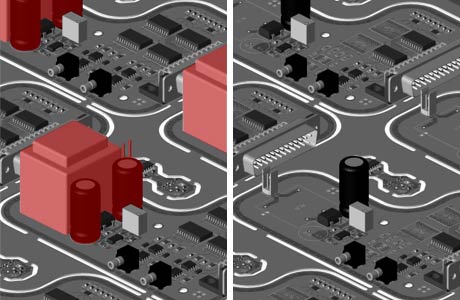

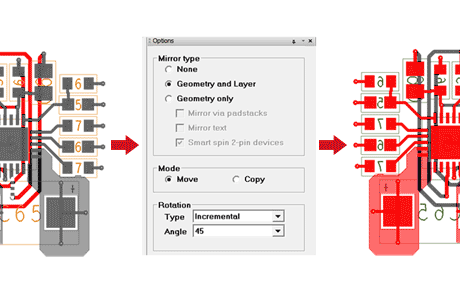

FlowCAD bietet eine Reihe von nützlichen Tool-Erweiterungen, die die Produktivität steigern. Diese Erweiterungen wurden entwickelt, um die spezifischen Bedürfnisse unserer Kunden zu erfüllen. FlowCAD programmiert gerne zusätzliche Funktionen, um auch Ihre speziellen Anforderungen zu erfüllen.

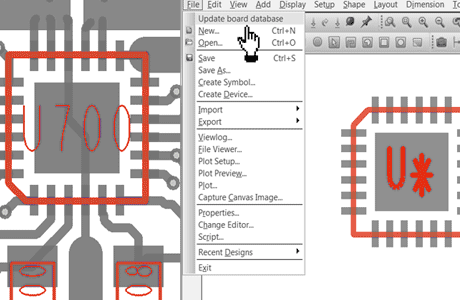

Die Installation der FloWare Module ist ein einfacher Vorgang und erfordert keine Fachkenntnisse. Der Installationsprozess umfasst einen Assistenten, der durch den FloWare-Installationsprozess führt. Menüstrukturen werden vom PCB Editor automatisch erkannt und in der Symbolleiste angezeigt.

Wählen Sie ganz nach Bedarf aus den verfügbaren Modulen und steigern Sie mit den Zusatzfunktionen die Produktivität beim PCB Design. Die Lizenz wird per E-Mail verteilt und gilt für den Standort Ihres Unternehmensstandortes. Jedes Modul beinhaltet eine ausführliche Dokumentation.